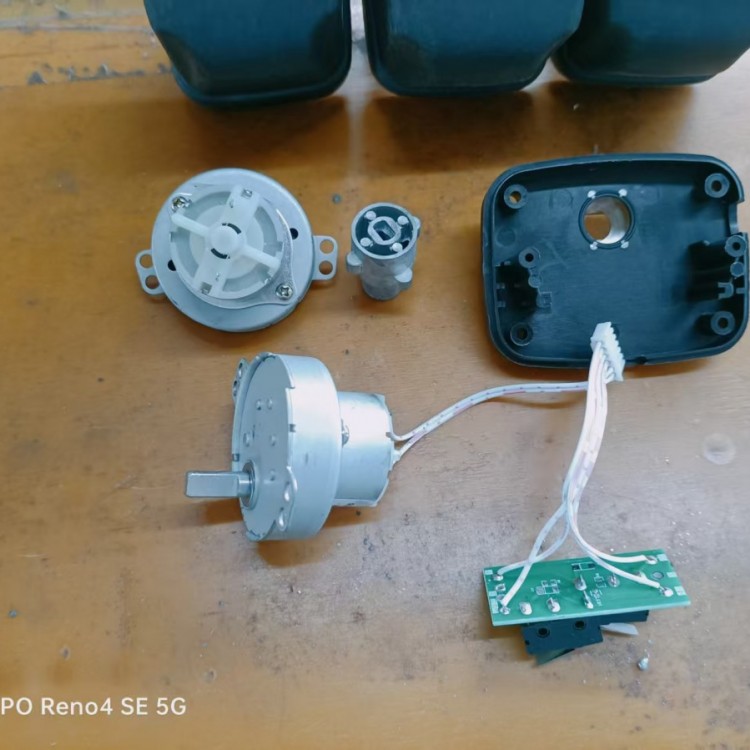

The unit employs a single-chip solution, with the CPU incorporating Flash ROM, RAM, EEPROM, ADC, timers, serial ports, and all other microcomputer protection resources. The entire unit does not use a chip bus; connections to external devices are realized through highly capable IO ports, and multiple isolation measures are employed to minimize the number of components, ensuring stable and reliable operation with strong anti-interference capability.

The device features six programmable input functions, allowing direct connection to the protection unit for both the transformer's inherent protection and various switch states. Post-protection action, the corresponding transformer inherent protection fault information is displayed in Chinese characters.

The device features a one-time molding engineering plastic structure, with a simple and reasonable shell design that is aesthetically pleasing. It is suitable for installation on medium and large-sized high-voltage switch cabinets.

The hardware design strictly separates low and high voltage. The low voltage section is mounted on the mainboard, with all signal lines shielded through the ground wire; the high voltage section is mounted on two bottom plates, with short wiring and wide spacing.

All connections to the outside are isolated, with switch quantity inputs, outputs, and communication interfaces optically isolated, analog quantities isolated through transformers, and outputs isolated via relays, reducing interference coming through the input/output lines.

The input/output sections of the analog signal through transformers, the input/output sections of the switching power supply, and the switching input section all employ shielding measures against high-frequency interference, effectively blocking high-frequency disturbances.

The simulation input, switch input, power input, and communication interface sections all utilize specialized components resistant to rapid transient disturbances, making the device particularly robust against transient interference.

The internal mechanism employs a high-precision clock chip, which integrates a backup battery and oscillator. The clock can accurately keep time for over a decade even after the device is powered off. The chip manufacturer guarantees an annual error of no more than 2 minutes, resolving the issue of inaccurate timekeeping during the device's independent operation, allowing for precise recording of various fault information.

The device features a three-level watchdog system, including external hardware watchdog, CPU hardware timer watchdog, and software watchdog. These different watchdogs monitor each other, ensuring the device does not crash under any circumstances.

The large-screen Chinese LCD display and menu operation provide a user-friendly interface. Setpoint data, control word meanings, and fault information are all displayed in Chinese characters, making fine-tuning and debugging very convenient.

The device internally features a large-capacity NVSRAM, allowing it to record up to 180 fault records in the first-in-first-out order, each with detailed timestamps and all current values, simplifying and facilitating fault analysis.

The software of the device is modularly designed, with all timing-limit protection module program codes shared. Critical program segments have multiple redundancy measures and have undergone long-term field operation tests, ensuring stable and reliable program performance.

The device features RS485 or RS232 communication interfaces with high-speed opto-isolation, employs the national standard Modbus protocol, and can upload various information to an automated monitoring system.